linux

软件测试

全志

二次元

技术美术

进程

AppCube

二维数组

decodeByteArray

消息传递

网络工程师

insert into

java-ee

可用性测试

filter

IL汇编

Async注解失效

西枢纽

面经

跳动爱心

IC验证

2024/4/12 4:00:50最全的一篇文章,介绍i2c总线的概念和特性,一看就会

本文内容:i2c总线的由来:i2c总线的一些特性:i2c的优点:i2c总线的规范i2c总线的概念总体特征i2c总线的由来:

在消费者电子、电讯和工业电子钟,看上去不相关的设计里经常有很多相似的地方。例如,…

UVM项目笔记——通过寄存器模型实现AHB接口的寄存器读写(内含源码)

目录 1.前言

2.DRIVER实现

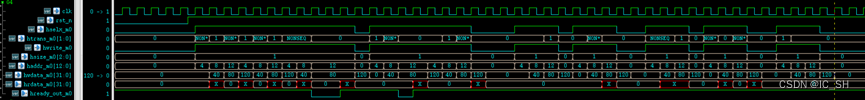

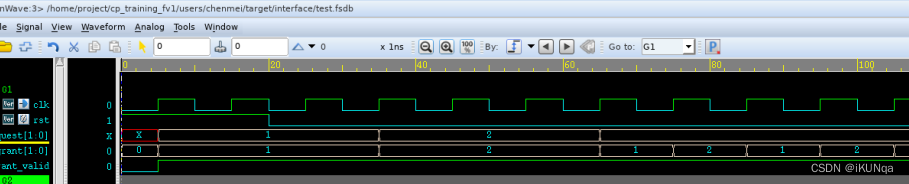

2.1 AHB二级流水时序

2.2 “队列错位法”实现driver

2.3 driver代码

2.4 仿真log与波形

2.5 多级流水拓展方法 1.前言

UVM driver在接口协议的实现中起着非常重要的作用,因为它一端处理基于类的事务级sequence,另一端处…

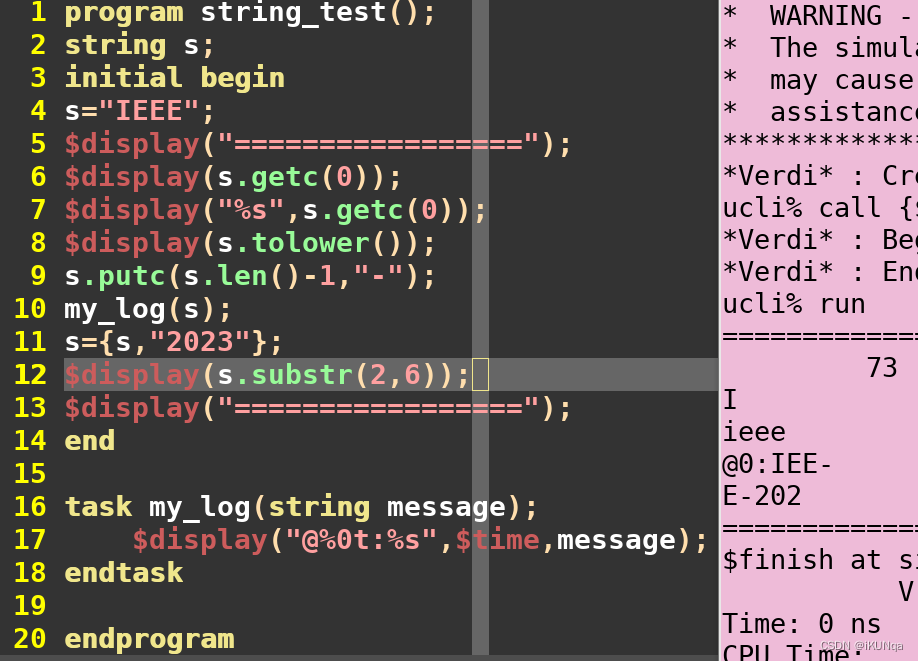

VCS第一讲:vcs和verdi演示一个简单的验证case

vcs软件使用方法和verdi怎么使用?

首先需要先成功安装好vcs软件和verdi软件; (如果没有软件,可以私信我,拒绝白嫖) 确认方法:

①在terminal中输入vcs,不会提示缺少license,如下图所示: ②命令行,输入verdi,如下显示 如果没报错,就说明vcs和verdi已经成功安装…

【sequence进阶 config_db message_2024.03.14】

sequence进阶

sequence的仲裁

多个sequence发送给一个sequencer的情况,使用的两种方式:

class virtual_seqence extends uvm_sequence;virtual task body();sub_sequene seq_0;sub_sequene seq_1;//第一种方式p_sequencer.apb_mst_sqr.set_arbitratio…

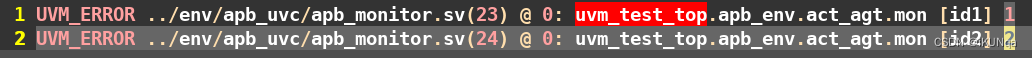

uvm中transaction的response和id的解读

在公司写代码的时候发现前辈有一段这样的代码:

....//其他transaction

uvm_create(trans);........

uvm_send(trans);

tmp_id trans.get_transaction_id();

get_response(rsp,tmp_id);

如果前面有其他transaction,这段代码里的get_response不带id的话…

入行IC| 数字IC设计和验证哪个好?(内含薪资对比)

网上有一个很火的问题那就是数字IC设计和验证哪个好?接下来我们从以下几个维度来对比一下这两个岗位。

入行门槛 从上述对比就可以看出,IC设计要比验证门槛高。

具体工作内容有哪些?

数字IC前端设计

1.配合芯片架构的设计;一…

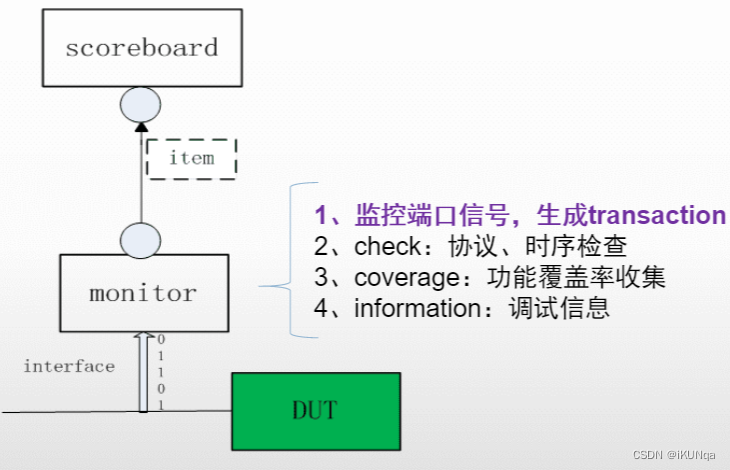

【APB协议 UVM_Sequencer Driver Monitor_2024.03.04】

apb协议

写时序

地址、写信号、PSEL、写数据信号同时发生变化,即传输的第一个时钟被称为SETUP周期。在下个时钟上升沿,PENABLE信号拉高,表示ENABLE周期,在该周期内,数据、地址以及控制信号都必须保持有效。整个写传输在这个周期…

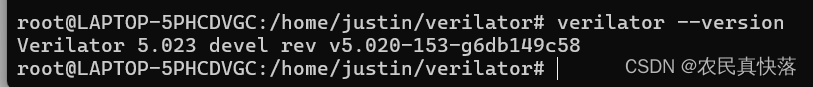

【IC设计】Windows和Ubuntu下安装Verilator

文章目录 Windows下安装verilatorUbuntu下安装verilator安装前的准备安装verilator检查 Windows下安装verilator

windows下安装比较麻烦,需要首先安装cygwin,cygwin是一个包管理工具,类似apt,然后通过cygwin安装verilator所需的各…

【SV的激励时序与接口_2023.12.26】

SV的激励时序

竞争冒险

竞争:由于每条途径延迟时间不同 冒险:竞争有先有后产生毛刺

解决方法:

仿真时,一般采用加#0延时,多个#0无法判定→非阻塞赋值

层次化事件队列

仿真器对一个timeslot内语句的执行是按照一定…

HDLBits-Verilog学习记录 | Verilog Language-Basics(1)

文章目录 3.Simple wire4.Four wires5.inverter | Notgate6. And gate7.Nor gate8.Xnorgate 3.Simple wire

problem:Create a module with one input and one output that behaves like a wire.

module top_module( input in, output out );assign out in;endmodule4.Four w…

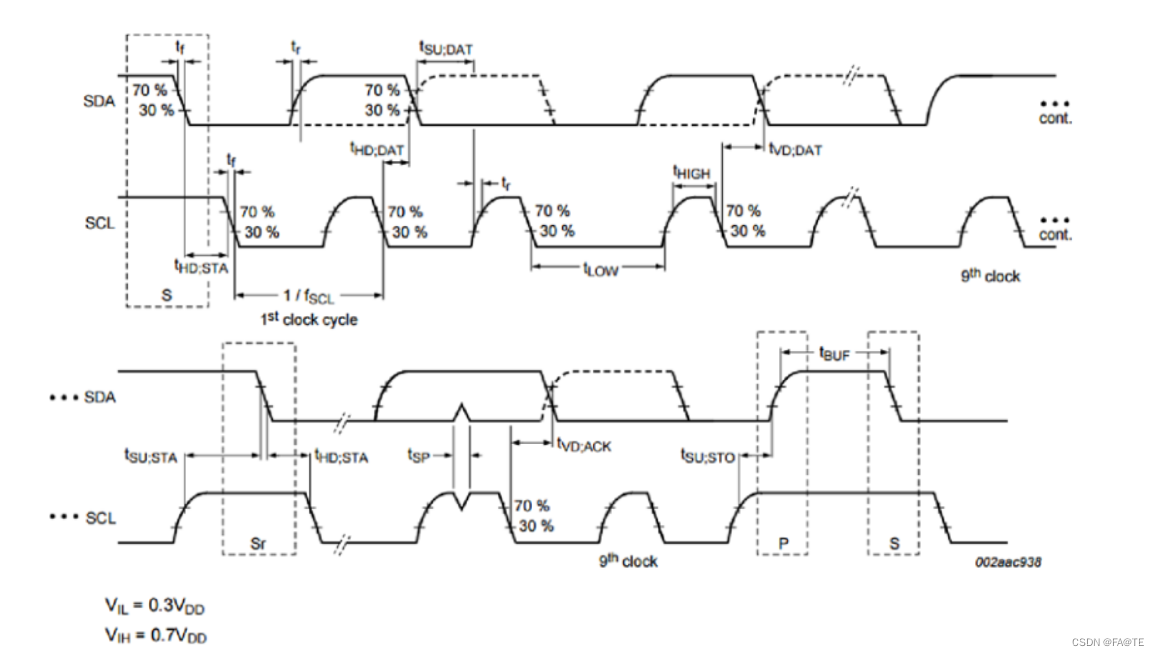

I2C 验证中需要注意的问题

I2C验证中需要注意的问题 1.NACK出现的时刻2.Restart和Start区别3.保持时间(Thd) 1.NACK出现的时刻

通常,在Master访问到错误的Device ID时,Slave会返回Nack,表示访问失败。此外,在Master对Slave读访问时&…

数字IC验证高频面试问题整理—附答案(三)

最近大家无不在讨论IC秋招,秋招想必缺的就是面试题目了。这不就来了~

共150道验证高频面试题整理~含答案(文末可领取全部题目)

Q1.二进制码、格雷码、独热码的特点

二进制码:基本的机器语言,每一位只能是0或1&…

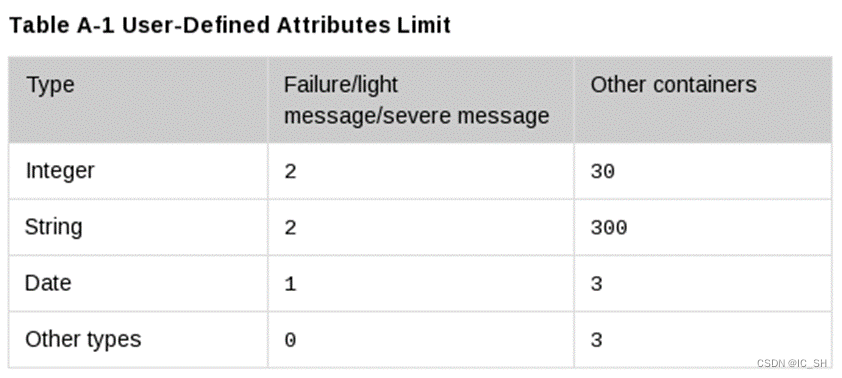

Cadence Vmanager vsif文件编写指南(持续更新...)

目录 1.NTF格式介绍

1.1.1 {属性:值}定义

1.1.2类别

1.1.3语法

2.vsif文件中有效的container

2.1 session {…} 1.NTF格式介绍

Cadence的Vmanager工具采用vsif类型的文件作为regression的输入文件,采用vplanx/csv类型的文件作为vplan的输入文件&am…

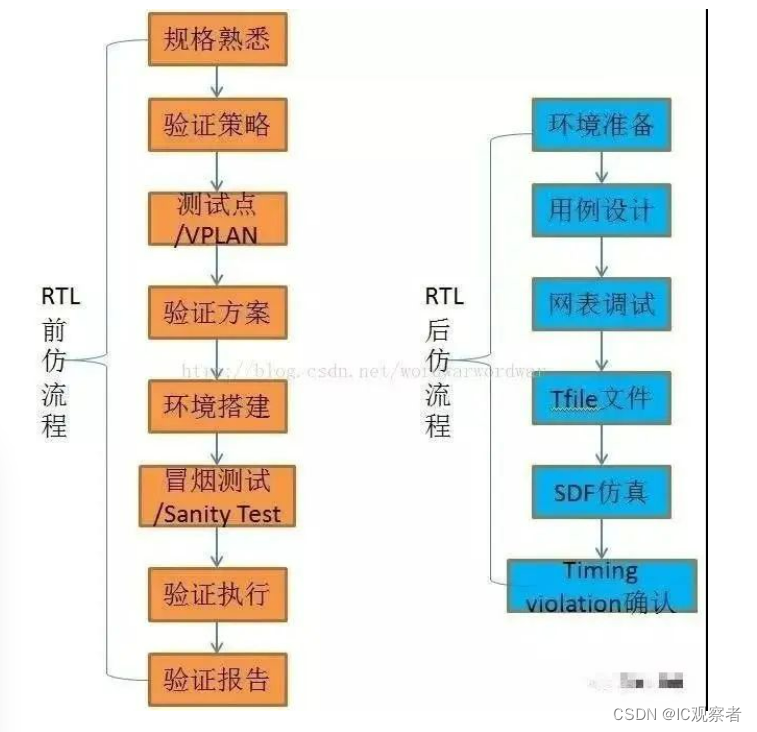

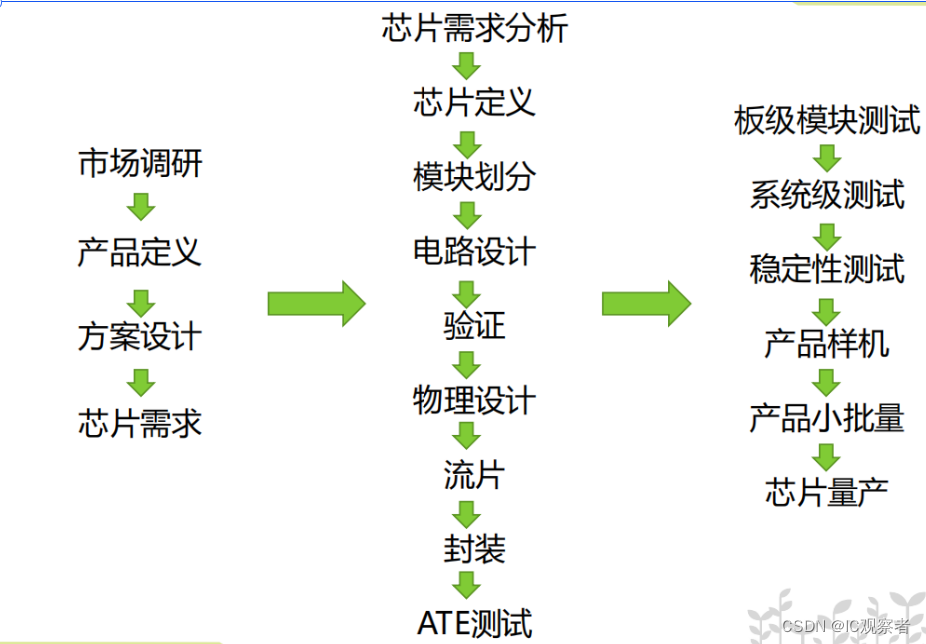

数字IC芯片验证流程及验证工具推荐?收藏专用

验证其实是一个“证伪”的过程,从流程到工具,验证工程师的终极目的都只有一个:

发现所有BUG,或者证明没有BUG,以保证芯片功能性能的正确性和可靠性。

验证环节对于一颗芯片的重要性也是不言而喻的:

从项…

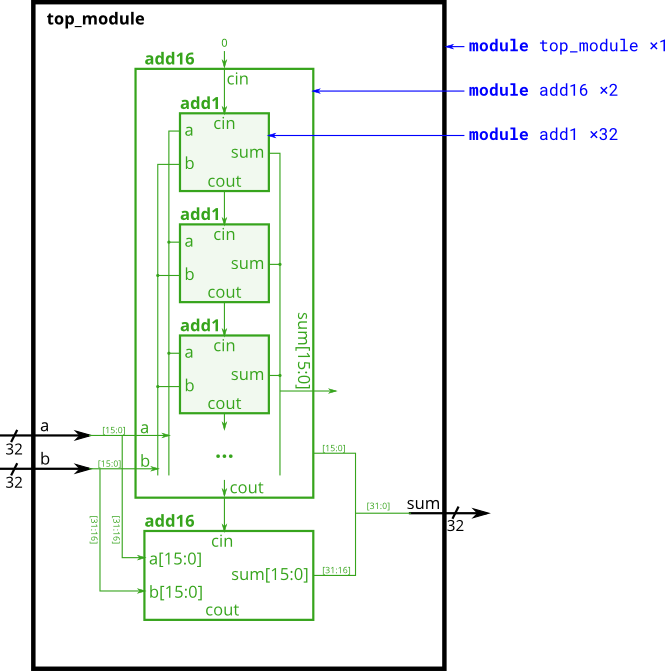

HDLBits-Verilog学习记录 | Verilog Language-Modules(2)

文章目录 25.Adder 1 | Module add26.Adder 2 | Module fadd27.Carry-select adder28.Adder-subtractor 25.Adder 1 | Module add

practice: You are given a module add16 that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. O…

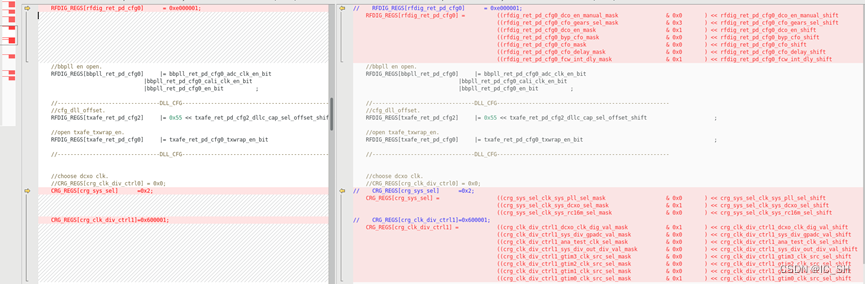

IC验证——perl脚本ccode_standard——c代码寄存器配置标准化

目录 1 脚本名称

2 脚本路径

3 脚本参数说明

4 脚本操作说明

5 脚本代码 1 脚本名称

ccode_standard

2 脚本路径

/scripts/bin/ccode_standard

3 脚本参数说明 次序 参数名 说明 1 address (./rfdig;.;..;./boot) 指定脚本执行路…

芯片验证学习实验1-全加器仿真操作学习,用vcs和verdi实操,有源代码

软件:vcs-2016,verdi-2016 系统:linu系统 本文目录: 1、设计代码2、验证代码3、filelist文件4、makefile脚本5、仿真调试1)在命令行输入 make run,进行仿真;2)输入 make verdi,打开波形;6、清理文件代码源码:

1、设计代码

在命令行敲入 gvim full_adder.v,然后把…

matlab 一些画图法总结(持续更新)

*****************************************画Dmd_L极坐标表示法**************************************** if(~exist(Dmd_L_array)) Dmd_L_array []; end Dmd_L_array [Dmd_L_array; Dmd_L]; thetaangle(Dmd_L_array); rabs(Dmd_L_array); polarplot(theta,r,o); *****…

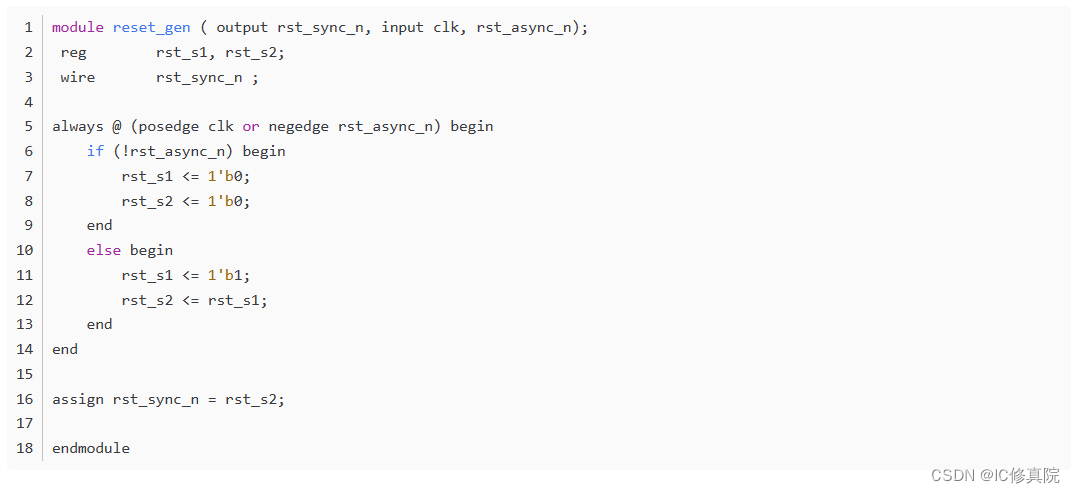

数字IC设计方法学:内容导航

目录1. 介绍2. 技能篇● Verilog● 数字电路基础● 时钟复位设计● 亚稳态设计● 低功耗设计● Systemverilog● Linux● TCL● VCS● Python/C● SVN3. 技术篇● RTL Design Flow● 综合逻辑综合工具Design Compile(DC)形式验证工具Formality时序分析工…

ic验证的主要工作流程和验证工具是什么?

验证其实是一个“证伪”的过程,从流程到工具,验证工程师的终极目的都只有一个:

发现所有BUG,或者证明没有BUG,以保证芯片功能性能的正确性和可靠性。

验证环节对于一颗芯片的重要性也是不言而喻的:

从项…

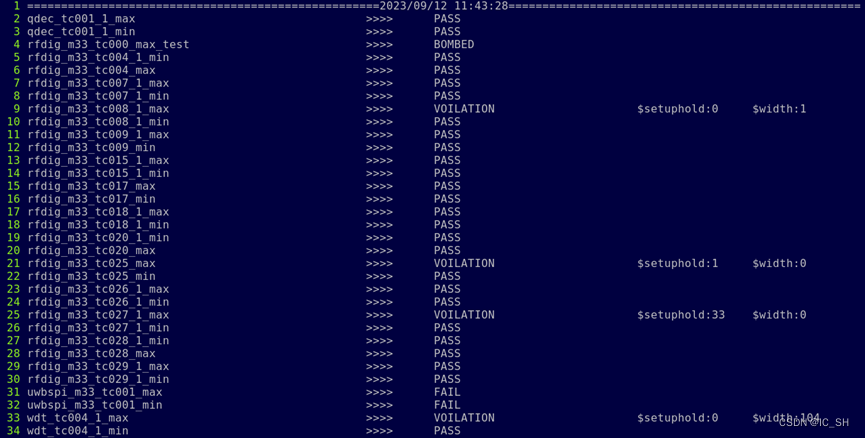

【IC验证】perl脚本——分析前/后仿用例回归情况

目录 1 脚本名称

2 脚本使用说明

3 nocare_list文件示例

4 脚本执行方法

5 postsim_result.log文件示例

6 脚本代码 1 脚本名称

post_analysis

2 脚本使用说明

help:打印脚本说明信息

命令:post_analysis help

前/后仿结束后,首先填…

静态时序分析(Static Timing Analysis, STA):内容导航

目录1. 介绍1.1. 局限性2. STA基本元素3. STA标准单元库4. STA环境5. STA时序检查6. STA接口分析7. STA鲁棒性检查静态时序分析(Static Timing Analysis, STA)是用来验证数字设计时序的技术之一,也是数字IC设计者必备的设计技能。

本专栏blo…

芯片SoC设计你了解吗?

数字IC设计根据岗位性质一般包含SOC设计,前端设计,ASIC设计,逻辑设计,IP设计,CPU设计等。 有人说:做IP设计就是翻译官,做SOC设计就是连连看。 SoC设计是做什么的?与IP设计有什么不同…

IC设计端各岗位薪酬对比(建议收藏)

根据人才招聘平台对于2023年已有数据统计,芯片工程师岗位均薪为26012元,位列全行业第一。

这里需要说明一下,这里的“芯片工程师”涵盖了设计、制造、封测等多环节岗位。并非只有芯片设计岗。 从行业招聘薪酬同比增速来看,电子技…

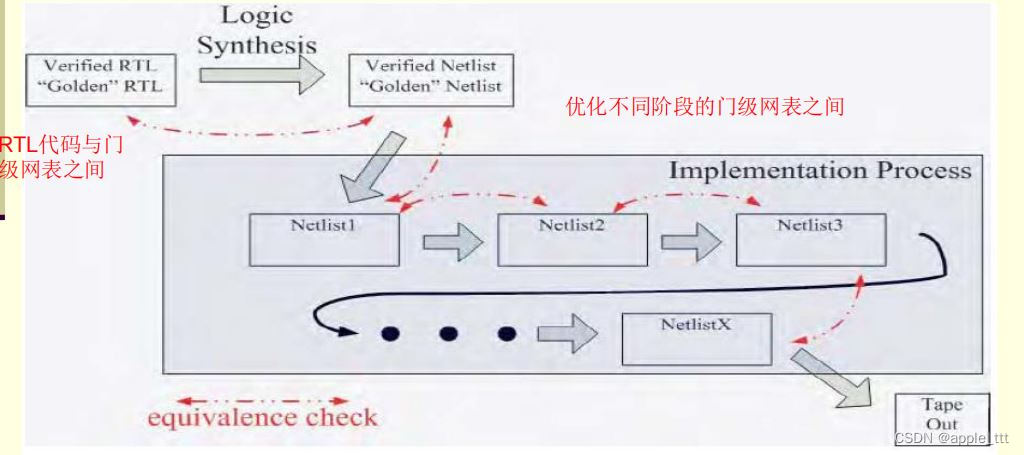

仿真验证方法(2)——静态验证

一、静态验证

1.1 概述 在之前的文章中,我们介绍了动态仿真,但是动态仿真用于百万门以上电路时所需时间极长,而且其功能覆盖率取决于所设计的输入激励向量,很难达到100%,因此静态时序分析和等效性检查这样的静态验证是…

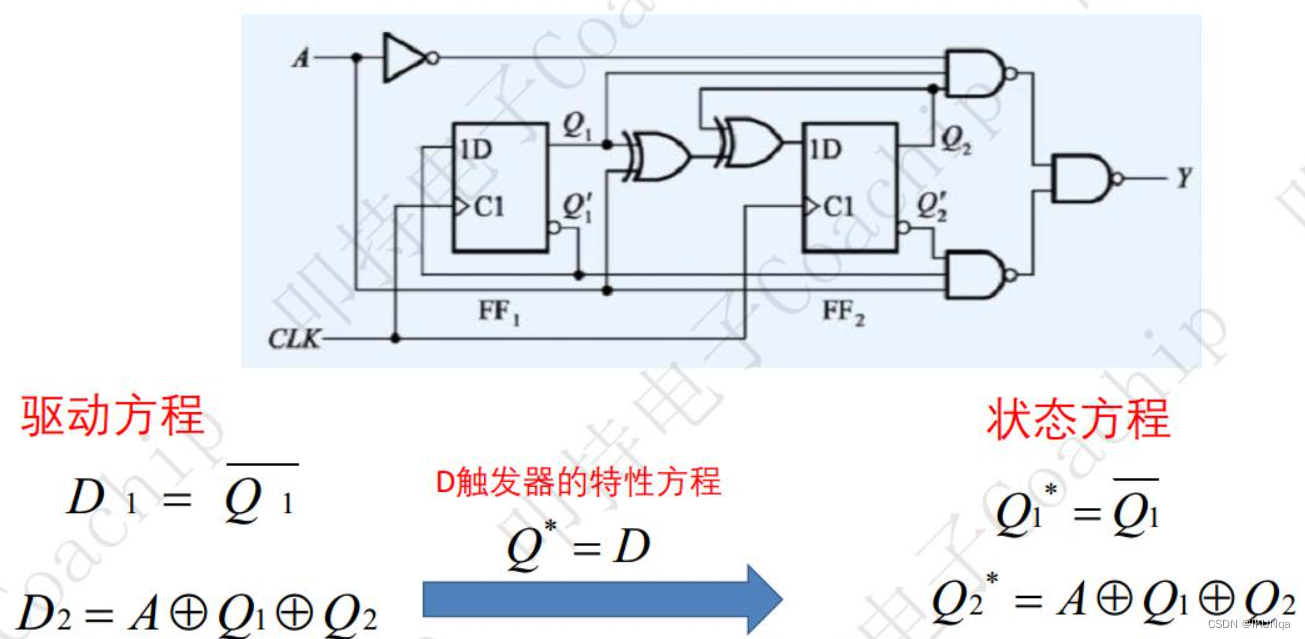

【数电知识点_2023.10.28】

数制与码制

十进制转二进制

8 bits 1 Byte 2|12 //121100自下而上 商为0为止 2|_ 6_…0 2|_ 3_…0 2|1…1 0…1 0.375 //0.3750.011自上而下 小数点为0为止 x 2 ———— 0.75…0 x 2 ———— 1.5…1 x 2 ———— 1…1

BCD码:每4位二进制表示一位十进制

8421…

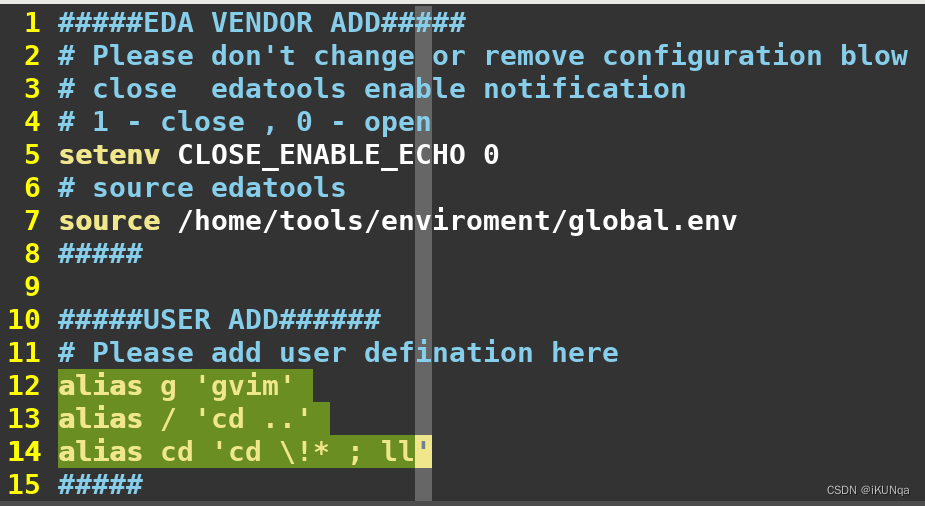

【EDA工具-VCS和Verdi的使用_2023.12.9】

芯片开发所需工具环境

Linux/Unix 编辑器Vim/Gvim EDA工具 Makefile 脚本语言Perl/Python 版本控制SVN/GIT

脚本语言Makefile

形式(由一系列的规则组成)

规则的目标:规则的依赖(可有可无) 规则的命令行(…

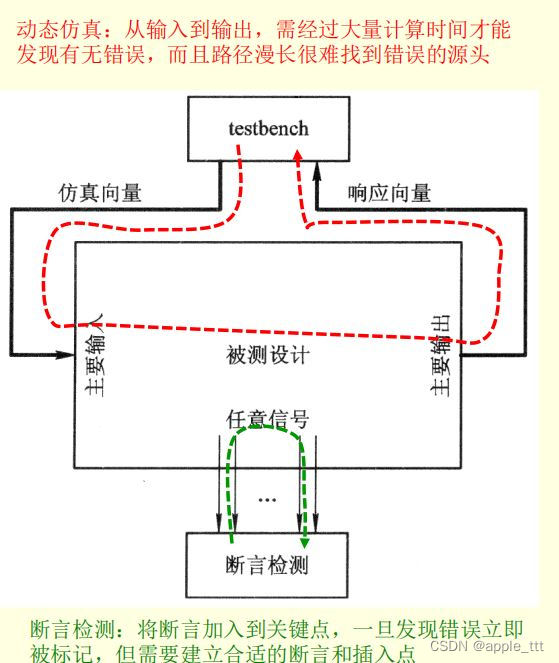

仿真验证方法(1)——动态验证

一、概述

1.1 验证的目的和方法 在现代集成电路设计中,验证所占工作量超过70%。验证要求真实而完备,它决定了设计的成败与成本。 验证的目的 原始描述是否正确?(代码) 逻辑功能是否正确?(功能…

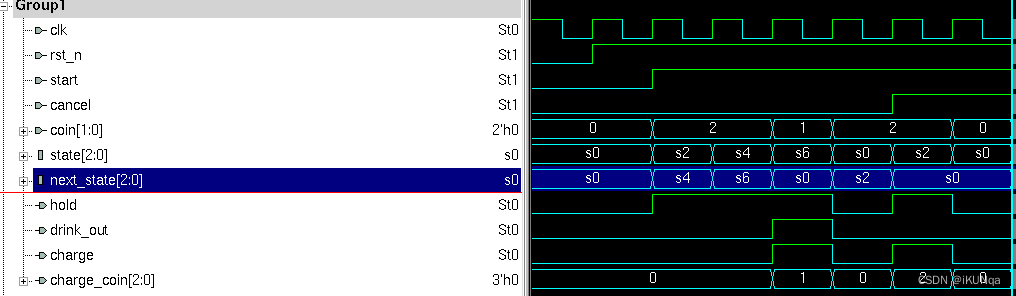

【状态机FSM 序列检测 饮料机_2023.12.1】

同步状态机

概念

同步状态机(同一脉冲边沿触发):有限个离散状态及某状之间的转移 异步状态机无法综合

分类

Moore状态机 只和状态有关,与输入无关 Mealy状态机 和状态和输入都有关 Mealy型比Moore型少一个状态

结构

由状态寄…

【验证概括 SV的数据类型_2023.12.18】

验证概括

验证的过程是保证芯片实现符合规格说明书(Specification,spec)的过程 验证的两项任务: RTL sim:前仿真,验证功能 GLS-Gate (Level Simulation):后仿真,验证功能和时序

验…

IC验证工程师工作一周年的体会

转眼之间自己已经工作一周年了,作为一名验证工程师,这一年里面感觉自己虽然有了一定的成长,但是成长的还是比较缓慢的,接下来从个人的角度说说我现在对从IC验证的一些体会。 一.要养成良好的工作习惯 (1)自…